YaccEqu

YaccEqu

Macintosh · PDF

| Filename | YaccEqu.pdf |

|---|---|

| Size | 0.31 MB |

| Subsection | prototypes / 1985_YACC / firmware |

| Downloads | 3 |

Contents

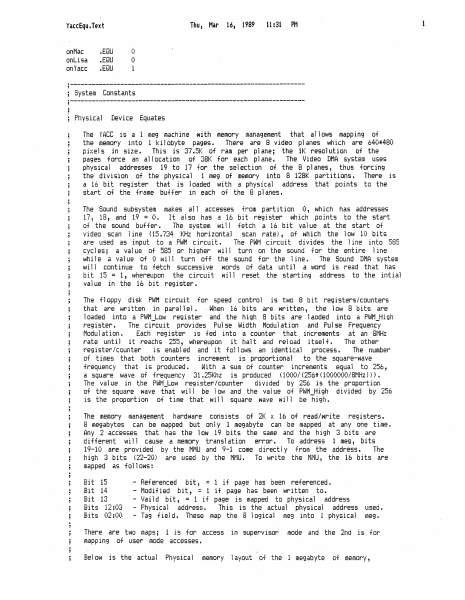

Thu, Mar

YaccEqu.Text

on Mac

onlisa

on Yacc

.EQU

.EQU

.EQU

16, 1989

11 :31

PM

0

0

'·----------------------------------------------------------------; System Constants

;----------------------------------------------------------------Physical

Device Equates

The YACC is a

meg machine with memory management that aliorJs mapping of

the memory into 1 kilobyte pages.

There are 8 video p1anes which are 640*480

pi;.~eis in size.

This is 37.5K of ram per plane; the 1K resolution of the

pages force an allocation of 38K for each plane.

The Video DMA system uses

physical addresses 19 to 17 for the selection of the 8 planes, thus forcing

the division of the physical 1 meg of memory into 8 128K partitions. There is

a 16 bit register that is 1oaded with a physical address that points to the

start of the frame buff er in each of the 8 p1anes.

The Sound subsystem makes al 1 accesses from partition O, which has addresses

17, 18, and 19 = .(i. It ai so has a 16 bit register i·Jh ich points to the start

of the sound buffer.

The system rJi 11 fetch a 16 bit value at the start of

video scan 1ine (15.734 KHz horizontal scan rate), of ~~hich the low 10 bits

are used as input to a PWM c irwi t.

The PvJM circuit di vi des the line into 585

cycies; a value of 585 or higher will turn on the sound for the entire i ine

whi 1e a value of 0 rJi 11 turn off the sound for the 1ine.

The Sound DMA system

will continue to fetch successive words of data until a word is read that has

bit 15 = 1, whereupon the circuit rJi 11 reset the starting -:.iddress to the int iai

vai ue in the 16 bit register.

The floppy disk PliJM circuit for speed control is two 8 bit registers/counters

that are written in para1 lel. . When 16 bits are written, the lm:.s 8 bits are

loaded into a PWM Low register and the high 8 bits are laoded into a PWM High

register.

The circuit provides Pulse Width Modulation and Pulse Frequency

Modu1 at ion.

Each register is fed into a counter that increments at an 8MHz

rate until it reachs 255, ~·Jhereupon it hait and reload itself.

The other

registericounter

is enabied and it folim&Js an identical process.

The number

of times that both counters increment is proportional to the square-wave

frequency that is produced •

~Ji th a sum of counter increments

equa 1 to 256,

a square wave of frequency 31.25Khz is produced ( 1000/ \256* ( 1000000/BMHz))) •

The vaiue in the PWM_Low register/counter

divided by 256 is the proportion

of the square ~-Jave that rJiii be 'low and the vaiue of Pl>JM_High divided by 256

is the proportion of time that will square wave will be high.

The memory management hard~111are consists of 2K ;{ 16 of read/write registers.

8 megabytes can be mapped but only 1 megabyte can be mapped at any one time.

Any 2 accesses that has the l ow 19 bits the same and the high 3 bits are

different v4ill cause a memory translation error.

To address 1 meg, bits

19-10 are provided by the MMU and 9-1 come directly from the address.

The

high 3 bits (22-20) are used b…

Showing first 3,000 characters of 10,716 total. Open the full document →