Turbo Mac Hardware Memory Map

Turbo Mac Hardware Memory Map

Macintosh · PDF

| Filename | Turbo_Mac_Hardware_Memory_Map_19841017.pdf |

|---|---|

| Size | 0.97 MB |

| Subsection | prototypes / 1984_Turbo_Mac |

| Downloads | 3 |

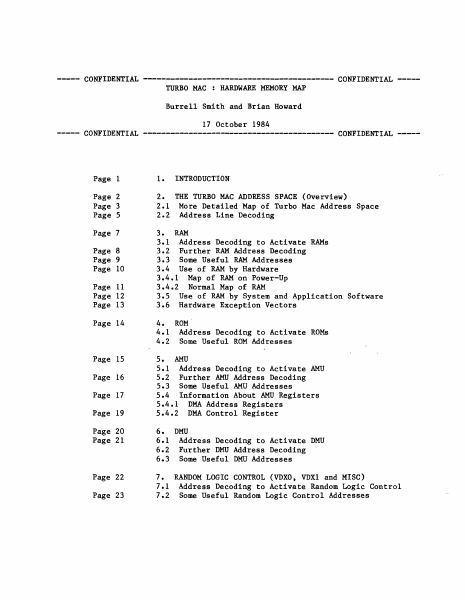

Contents

CONFIDENTIAL ------------------------------------------ CONFIDENTIAL

TURBO MAC : HARDWARE MEMORY MAP

Burrell Smith and Brian Howard

17 October 1984

CONFIDENTIAL ------------------------------------------ CONFIDENTIAL

INTRODUCTION

Page 1

1.

Page 2

Page 3

Page 5

2. THE TURBO MAC ADDRESS SPACE (Overview)

2.1 More Detailed Map of Turbo Mac Address Space

2.2 Address Line Decoding

Page 7

3. RAM

3.1 Address Decoding to Activate RAMs

Page 8

Page 9

Page 10

3.2 Further RAM Address Decoding

3.3 Some Useful RAM Addresses

3.4 Use of RAM by Hardware

3.4.1 Map of RAM on Power-Up

3.4.2 Normal Map of RAM

3.5 Use of RAM by System and Application Software

3.6 Hardware Exception Vectors

Page 11

Page 12

Page 13

Page 14

4.

4.1

4.2

Page 15

Page 16

Page 17

Page 19

Page 20

Page 21

Page 22

Page 23

ROM

Address Decoding to Activate ROMs

Some Useful ROM Addresses

AMU

Address Decoding to Activate AMU

Further AMU Address Decoding

Some Useful AMU Addresses

5.4 Information About AMU Registers

5.4.1 DMA Address Registers

5.4.2 DMA Control Register

5.

5.1

5.2

5.3

6.

6.1

6.2

6.3

DMU

Address Decoding to Activate DMU

Further DMU Address Decoding

Some Useful DMU Addresses

7. RANDOM LOGIC CONTROL (VDXO, VDXl and MISC)

7.1 Address Decoding to Activate Random Logic Control

7.2 Some Useful Random Logic Control Addresses

Turbo Mac Memory Map

17 October 1984

Page 24

Page 25

Page 26

Page 27

Page 28

Page 29

Page 30

Page 31

8. SCC

8.1 Address Decoding to Activate SCC

8.2 Further SCC Address Decoding

8.3 Some Useful SCC Addresses

9. IWM

9.1 Address Decoding to Activate IWM

9.2 Further IWM Address Decoding

9.3 Some Useful IWM Addresses

10. VIA

10.1 Address Decoding to Activate VIA

10.2 Further VIA Address Decoding

10.3 Some Useful VIA Addresses

10.4 Turbo-Mac-Specific Information about VIA Registers

10.4.1 Port A Input, Output, and Data Direction Registers

10.4.2 Port B Input, Output, and Data Direction Registers

10.4.3 Control Registers

10.4.4 Interrupt Flag and Enable Registers

Page 32

11.

AUTO-VECTOR "READ" ADDRESSES

Page 33

12.

SOME USEFUL DECODING EQUATIONS

Previous Document Versions:

1.

Page 1

19-5ep-84, 10-Sep-1984.

INTRODUCTION

The principle portions of Turbo Mac's address space consist of volatile

read/write memory (RAM) and permanent read-only memory (ROM). In addition to

RAM and ROM, several input/output functions are also selected using address

lines, so that they appear to occupy portions of the Turbo Mac "memory". These

include the 6522 Versatile Interface Adapter (VIA), the 8530 Serial

Communications Chip (SCC), the disk interface chip (IWM), the Address Management

Unit (AMU), the Data Management Unit (DMU) , and the Random Logic Control.

When the Turbo Mac is first turned on, ROM appears at the bottom (lowest

addresses) portion of the address space. This is useful for the ROM-stored

software which starts the system running. After startup, the OVERLAY signal

from the VIA is changed to a low (zero), mapping RAM into its normal place at

the bott…

Showing first 3,000 characters of 36,651 total. Open the full document →