BIGMAC Pgmrs Model 6 85

BIGMAC Pgmrs Model 6 85

Macintosh · PDF

| Filename | BIGMAC_Pgmrs_Model_6-85.pdf |

|---|---|

| Size | 0.26 MB |

| Subsection | prototypes / 1985_Big_Mac |

| Downloads | 1 |

Contents

Rich Page

6/29/85

Programmers Model for the Big Mac

Introduction

This document describes the Big Mac from the programmers view of

the machine which includes a description of the address space map, the

system registers and the decoding of the I/O devices and their registers.

The Big Mac MMU and decoding logic maps the 32 bit address space of the

68020 into two address spaces, one for RAM and the other for Screen, ROM

and I/O. There exists a 5 bit register named the High Decode Map register

which controls the position of the ROM and provides a mechanism to limit

the number of address bits used for decoding logical addresses. The HOM

register can'$rogrammed to cause the high address bits (those above A23)

to be significant to the decoding hardware. This allows a range of address

space sizes from 24 to 32 bits. In the smallest configuration, the address

space is limited to 16Mb and the upper eight bits are insignificant to

decoding which will allow software to use the upper eight bits as tags. In

the largest configuration, the address space is 4Gb and none of upper bits

~

__--==:::::::::::::==-:--

are available.

CJ (. ~:J

Address S pace Map

<z

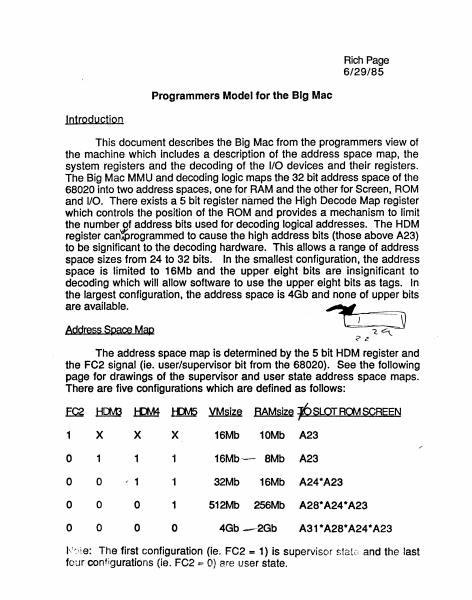

The address space map is determined by the 5 bit HOM register and

the FC2 signal (ie. user/supervisor bit from the 68020). See the following

page for drawings of the supervisor and user state address space maps.

There are five configurations which are defined as follows:

.EQg

HOO

!-Dy14

tpv15

VMsize

RAMsize t>S.LQr RaJ! SCREEN

1

x

x

x

16Mb

10Mb

A23

o

1

1

16Mb -- 8Mb

A23

o

o

,. 1

'1

32Mb

16Mb

A24 *A23

o

o

o

1

512Mb

256Mb

A28* A24 * A23

o

o

o

o

I\\~~te:

4Gb ---·2Gb

A31 *A28* A24 * A23

The first configuration (ie. FC2 = 1) is supervisor state and the last

four configurations (ie . FC2 == 0) are user state.

Rich Pege

6/21/85

-

Big Moc Address Spoce Map (~upervisor Stcte)

r

I/O

XXFOOOOO

SLOTS

XXFFOOO

XXFEOOO

System Regi ster-- ~-l

_.-

°

°

DMA

~T G.,S NO., RT

XXFDOOOO

XXDOOOOO

XXCOOOOO

XXBOOOOO

reserved

I--~--~

ROM h1gh

L----=~--~

re s erv ed

r--~--~

,

XXFCOOOO

XXFBOOOO

IWM

L..

SCC2

.....

SCC1

XXFAOOOO

"--

XXF90000

L....-

SCSI

SCREEN

XX90qOOO

XXSOOOOO

XX700000

XX60qooO

RAM

.:sou

C.l

\'=c>

I...--

-

]-

-".-

-'-..J

RAM

I---'--~

RAM

I----~

RAM

RAM

)()(SOO,OOO

I---'-~

XX40QPOO

RAM or ROM! low

I--=~~~

XX300POO

I---'-~

RAM

RAM

RAM

)()(OOOOOO

MMU

XFOOOOO

I~

\

.c., F.D.B

_I\fi

RAM or ROM zero

-.....,/.---~~~-

-

:

~ -~~~ Q<~~~~

-- /

R1Ch Page

6/21/85

Big M8C Address Sp8ce M8P (User State)

.,.........

FFFOOOOO

FFEOOOOO

FFDOOOOO

FFCOOOOO

FFBOOOOO

FFAOOOOO .

I/O

SLOTS

FFFFOOOO

FFFEOOOO

FFFDOOOO

reserved

ROM high

reserved

FFFCOOOO

FFFBOOOO

FFFAOOOO

FFF90000

00600000

00500000

00400000

00300000

00200000

00100000

00000000

DMA

VTG,SND ,RTC,FDB

IWM

SCC2

SCCl

SCSI

._---,-

SCREEN

FFFOOOOO

00700000

System Regi ster

RAM

RAM

RAM

RAM or ROM low

RAM

RAM

RAM

RAM or ROM zero

MMU

--

Note: The bi ts HDM3, HDM4 and HDM5

define t…

Showing first 3,000 characters of 6,241 total. Open the full document →